目前的电子产品市场竞争非常激烈,厂商都希望能在最短时间内将新产品推出市场,以致子系统的设计周期越缩越短。在这个发展过程中,FPGA及ASIC的重要性越来越受到重视,因为新系统的很多重要功能往往需要由它们来实现。在FPGA系统设计中,电源管理是尤其需要慎重考虑的关键问题之一。要为FPGA提供稳定的供电,需要全面审视系统的整体供电需要。文中提到的方法也同样适用于ASIC。

考虑到复杂的起始条件、瞬态行为及开关规格等诸多因素,电源供应系统必须符合一定的要求,这一点极为重要。器件中电源的旁路或去耦问题也需要特别重视。典型的FPGA电源管理需求如图1所示。一般来说,FPGA最少需要两个电压为其提供供电:一个专为“核心”供电(1.0~2.5V[典型值]),另一个专为输入/输出供电(3.3V[典型值])。许多FPGA另外还需要第三个低噪音、低纹波的电压,以便为辅助电路供电。不同系列的FPGA有不同的电压需要,典型电压为2.5V或3.3V。对每一电压来说,工作电流并不固定,而是取决于许多与实际应用相关的因素,例如FPGA的速度及资源利用率等。工作电流可以低至100mA,也可高至20A。在这些系统中,输入电压通常比FPGA的任一供电电压都要高,因此需要降低其电压并加以稳压。在FPGA中最常用的三款降压稳压器电路如图2所示,分别是同步降压稳压器、非同步降压稳压器及线性稳压器。选用稳压器时,必须详细考虑系统的规格要求及稳压器的工作情况,以便作出配合。为了得到成功的设计,也需要考虑以下的问题。

图 1 典型的FPGA或ASIC电源管理需求

图 2 降压稳压器结构

输入电压(VIN)

FPGA的输入供电由银盒、底板或中间供电干线提供。典型的输入电压一般介于3~15V之间,部分工业应用系统的输入电压会高达30V。输入电压中的一部分可能用不到,这是因为,为芯片供电的稳压器的VIN引脚上有最大额定值的限制。

输出电压(VOUT)及

输出电流(IOUT)

稳压器的主要作用是稳定电压,换言之,无论输入电压及负载电流如何波动,稳压器都可以产生固定的输出电压。正如先前所说,工作电流可以在100mA~20A之间的范围内变化。输入电压、输出电压及输出电流等数值一经确定后,便可决定应该选用哪种类型的稳压器。以下是从经验或实践中得出的一些结论:

* 假如功耗不超过1W,应采用线性稳压器;

* 假如输入/输出电压比小于2:1,而输出电流不超过3A,应采用非同步降压稳压器;

* 假如输入/输出电压比大于2:1,而输出电流又超过5A,应采用同步降压稳压器。

稳压器通过将参考电压与出现在反馈引脚上的小部分输出电压加以比较来稳定输出电压。参考电压通常设置为可得到的最小输出电压。

部分控制器规定启动时间不能超过某一时限,这使得稳压器无法将输入电压降低太多。控制器的最小启动时间(TON min)也限定了一定频率下的最小输出电压。例如,如果启动时间超过其最低时限,输出电压便会升高超过预期值。

VIN=12V

VOUT=1.2V

D=1.2V/12V=0.1

FS=300KHZ

Ton min=0.1*(1/300KHZ)=333ns

图3 排序及跟踪方案

降低开关频率有助提升降压比。

开关稳压器的工作频率

开关频率的高低会影响一些重要的参数,包括电感和电容的大小、效率、纹波电压,以至解决方案的设定。开关频率较高时,设计工程师应选用较小的电感以及较小的输出电容,以便降低纹波电压。较高的开关频率也使得高带宽系统的设计易于实现。此外,设计工程师可能也需要让系统工作于特定的频率波段以外,以避免杂波干扰,采用可调节频率的降压稳压器有助于提高系统设计的灵活性。

效率

效率是输出功率与输入功率的百分比,用于表示无用功率的大小。这是一个经常被系统设计工程师误解的参数。当输入电流无限制或是电池寿命无关紧要时,重要的就不仅仅只有效率,还有功耗。功耗会直接导致许多系统元件的温度上升,如芯片、MOSFET、电容以及电感。一定面积上的功耗也很重要。一般来说,在没有气流的条件下,一平方英寸的铜表面耗散1W的功率,会导致温度升高40℃。

例如,假设:

VOUT=1.5V

IOUT=15A

效率=90%

功耗=2.5W

这2.5W的功率若通过一平方英寸的铜耗散,铜的温度会升高100℃。

在另一例子中,有:

VOUT=1.5V

IOUT=1.5A

效率=81%

功耗=0.53W

若与前一例子中90%的效率相比,这个例子中的效率数字看起来不大理想。但在这个例子中,一平方英寸面积所耗散的功率只有0.53W,温度只会升高20℃。

这两个例子说明功耗比效率更为重要,系统设计工程师若明白这个道理,便可为其所设计的系统选择最理想的效率,降低系统的整体成本。

体积

在特定的设计中,缩小元件的面积或高度会对系统的成本及效率产生负面影响。例如,小型电感的等效串联电阻(ESR)通常都比大型电感高,采用低外形设计的电感或电解电容一般都较为昂贵,多层电路板可以缩小体积,但一般来说也会增加整体成本。一些设计工程师可能会通过提高开关频率的方法来缩小元件尺寸,但开关频率的提高会增加功率损耗。

系统成本

为FPGA芯片提供最具成本效益的供电一直是设计工程师的目标,但将供电成本尽量降低并不表示要选用最廉价的稳压器。例如,内置FET的稳压器较为昂贵,因此设计工程师有时会不假思索地拒绝采用这类稳压器,但在某些应用情况下,这类稳压器比外置MOSFET的稳压器更具成本效益。另外,外置FET的稳压器对于来自电路板的噪音影响更加敏感,而简单的内置MOSFET的集成开关稳压器能够消除大多数的噪音敏感性问题。

另一个例子是,应该采用双通道降压转换器取代两个单通道开关转换器。这样可以大大节省需要的输入电容数量,而且由于两个相位可以异相操作,因此输入电容的均方根(RMS)纹波电流可以大幅降低。如果多个非同步开关稳压器以略微不同的频率工作,就会产生拍频,而双相位控制器可以避免拍频。要知道,真正的成本是系统物料清单上所开列的成本,并不是个别元件的成本。

瞬态响应

在工作电流点上,FPGA的核心电压会产生极高的转换率。为此,控制器必须提供较大的阶跃负载电流,将输出电压的扰动减至最低。控制器对负载的响应能力被称为瞬态响应。瞬态响应会影响工作带宽、输出电容以及等效串联电阻。

排序及跟踪

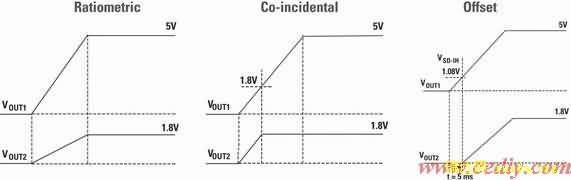

系统启动时,可能需要某一电源在另一电源之前启动,如果顺序不正确,电源便会锁死,而FPGA可能会因此受损或发生故障。有些FPGA在输入/输出电压和核心电压之间具有排序及/或跟踪功能,几种不同的排序及跟踪方法如图3所示。如果稳压器已经集成有电源正常(power good)、使能(enable)、软启动及跟踪功能,便可简单灵活地实现排序及跟踪;若没有,便需增加外部电路以确保电源可以按照正确的顺序启动。

启动

FPGA电压要求有一定的上升速率,这可以利用软启动电容实现。而且,启动时的上升电压一般都必须是单调的,不能下降。如果电源供应的输出电容较小,启动时的电压就会受其影响而下跌。容量足够大的电容可以储存充足的电荷,为FPGA芯片提供启动负载瞬态电压。

同步

同步功能的作用是确保两个或更多的稳压器可以一同被锁定在某一频率,以免出现拍频。

结语

由于不同的系统有不同的要求,再加上FPGA或ASIC的复杂性和利用率也不尽相同,因此,最佳的电源配置也各不相同。除了输入电压、输出电压及输出电流之外,也要考虑其他条件,如排序、跟踪及启动等的特别要求。另外,功耗、体积及成本也会对设计产生影响。■