��飺����������������TMS320F2812 ����Ѷ�Ŵ�������������ֿ�������Ƶ�DSP��������DSP ����������������ԣ���Ҫʹ����Ƕ��ʽ����Ӧ�ã������ֵ������(digital motor control, DMC)������ߢȡ��I/O ����(data acquisition and control, DAQ)���������Ӧ����ѻ�������Ч���̲�Ʒ�������ڣ�F28x ����֧��ȫ��CCS������C compiler���ṩC ������ֱ��Ƕ�������Եij������棬����C ���ԵĻ����д�����������д����ֵ��һ����ǣ�F28x DSP ����֧�������IQ-math ��ʽ�⣬ϵͳ������Ա����ʹ�ñ��˵Ķ�����DSP ����չ����ĸ��������㷨��F28x ϵ��DSPԤ�Ʒ�չ��400MHz��Ŀǰ�ѷ�չ��150MHz ��Flash ��ʽ��

1.�����ܾ�̬CMOS�Ƴɼ���

(1)150MHz(6.67ns����ʱ��)

(2)ʡ�����(1.8VCore��3.3VI/O)

(3)3.3V��ȡ�ɳ����ѹ

2.JTAGɨ��֧��

3.����32BitCPU

(1)16x16��32x32MAC Operations

(2)16x16Dual MAC

(3)�������߽ṹ

(4)�����ж���Ӧ

(5)4M���Գ���Ѱַ�ռ�(LinearProgramAddressReach)

(6)4M��������Ѱַ�ռ�(LinearDataAddressReach)

(7)TMS320F24X/LF240X������ļ���

4.оƬ��(On-Chip)���ڴ�

(1)128Kx16 Flash(4��8Kx16��6��16Kx16)

(2)1Kx16OTPROM(���οɳ���ֻ���洢��)

(3)L0��L1��2��4Kx16 SARAM

(4)H0��1��8Kx16SARAM

(5)M0��M1��2��1Kx16 SARAM

��128Kx16 Flash��18Kx16 SARAM

5.�ⲿ�ڴ�ӿ�

(1)֧��1M���ⲿ�ڴ�

(2)�ɳ����Wait States

(3)�ɳ����Read/Write StrobeTi��Сg

(4)����������оƬѡ��(Chip Selects)

6.Ƶ����ϵͳ����

(1)֧�ֶ�̬����λ����ģ��(PLL)���ʱ��

(2)On-Chip����

(3)���Ź���ʱ��ģ��

7.�����ⲿ�ж�

?8.��Χ�ж���չ����(PIE)��֧��45����Χ�ж�

9.128�������

(1)����Flash/ROM/OTP��L0/L1SARAM

(2)��ֹ��������

10.����32λCPU Timer

11.�綯��������Χ

(1)�����¼�����ģ��(EVA��EVB)

(2)��240xADSP����

12. (1)ͬ��������Χ�ӿ�SPIģ��

(2)�����첽����ͨѶ�ӿ�SCIģ�飬��UART

(3)eCAN(Enhanced Controller Area Network)

(4)McBSP With SPI Mode

13.16���ŵ�12λģ��-����ת��ģ��(ADC)

(1)2x8ͨ�������������

(2)����������ȡ��-����(Sample-and-Hold)��·

(3)�ɵ�һ��ͬ��ת��

(4)���ٵ�ת���ʣ�80ns/12.5MSPS

ͼ1TMS320F2812���ܷ���ͼ��

2.2TMS320F2812Ӳ���ṹ����

2.2.1OSC��PLL����

F2812оƬ�������һ����λ����ģ��(PLL)�����ģ�齫���ṩ����оƬ����Ƶ��Դ��PLLģ�鷽��ͼ��ͼ2��ʾ��PLL�ṩ��4 λ(PLLCR[3:0])��PLL����ѡ��10�ַŴ��ʣ��ɶ�̬�ı�CPU��Ƶ��Ƶ�ʡ����1��ʾΪPLLCR �������ĸ�ʽ����������λ˵�����2��ʾ��

XCLKIN���ⲿƵ��Դ���롣

OSCCLK����XCLKIN��Ƶ��һ����

CLKIN��CPUά���������������Ƶ��Դ����������оƬ�����Ƶ�ʡ�

SYSCLKOUT����CLKIN��Ƶ��һ�����ṩ����Χ��·ʹ�á�

ͼ2 OSC��PLL����ͼ��

��1PLLCR������λ��ʽ����

15-4 3 2 1 0 Reserved DIV R-0 R/W-0

R:��ȡ;R/W:�ɶ���д;-0=���ú��ֵ

NOTE:EALLOW-protected register

��2 PLLCR������λ˵������

λ ����

��������

15-4 Reserved ���� 3-0DIV DIV ���Կ���(����PLL�Ƿ�����·״̬�Կɿ���)���趨(����PLL Ϊ����·״̬ʱ�ſ��趨)PLL��Ƶ�ʱȣ�=0000��CLKIN =OSCCLK/2(PLL bypass)

=0001��CLKIN =(OSCCLK*1.0)/2

=0010��CLKIN =(OSCCLK*2.0)/2

=0011��CLKIN =(OSCCLK*3.0)/2

=0100��CLKIN =(OSCCLK*4.0)/2

=0101��CLKIN =(OSCCLK*5.0)/2

=0110��CLKIN =(OSCCLK*6.0)/2

=0111��CLKIN =(OSCCLK*7.0)/2

=1000��CLKIN =(OSCCLK*8.0)/2

=1001��CLKIN =(OSCCLK*9.0)/2

=1010��CLKIN =(OSCCLK*10.0)/2

=1011-1111 ������

2.2.2ϵͳƵ�ʿ���

��ͼ3��ʾ��������Χ��·��Ƶ�ʶ�����SYSCLKOUT������Ƶ��

����F2812��������Χ�ֳ����࣬�ֱ��ǣ�

1.������Χ�������¼�����ģ��(EVA��EVB)��ADC��

2.������������SCI-A/B��SPI��McBSP��

HSPCLK��������Χ��Ƶ�ʣ��ɾ���HISPCP�������ı���Ƶ�ʣ����

2-3��ʾΪHISPCP�������ĸ�ʽ����������λ˵�����4��ʾ��

LSPCLK��������Χ��Ƶ�ʣ��ɾ���LOSPCP�������ı���Ƶ�ʣ����

2-5��ʾΪLOSPCP�������ĸ�ʽ����������λ˵�����6��ʾ��

��3HISPCP������λԪ��ʽ����

15-3 2 1 0 Reserved HSPCLK R-0 R/W-001

R:��ȡ;R/W:�ɶ���д;-0=���ú��ֵ

NOTE:EALLOW-protected register

��4 HISPCP ������λԪ˵������

λԪ����

��������

15-3 Reserved ���� 2-0HSPCLK��ЩλԪ�趨������ΧƵ�ʱ�(HSPCLK)��SYSCLKOUT�Ĺ�ϵ�����HISPCP��0��HSPCLK=SYSCLKOUT/(HISPCPx2)

���HISPCP=0��HSPCLK =SYSCLKOUT

=000������Ƶ��= SYSCLKOUT/1

=001������Ƶ��= SYSCLKOUT/2( Ԥ��ֵ)

=010������Ƶ��= SYSCLKOUT/4

=011 ������Ƶ��= SYSCLKOUT/6

=100������Ƶ��= SYSCLKOUT/8

=101������Ƶ��= SYSCLKOUT/10

=110 ������Ƶ��= SYSCLKOUT/12

=111 ������Ƶ��= SYSCLKOUT/14

��5 LOSPCP������λԪ��ʽͼ��

15-3 2 1 0 Reserved LSPCLK R-0 R/W-010

ͼ7 CPU-Timers ����ͼ

2.5�¼�����ģ��(EVA,EVB)

��ͼ8�¼�����ģ�����һ����;��ʱ��(General-Purpose,GPTimers)��ȫ�Ƚ�(full-compare)/PWM ��Ԫ����ץ��Ԫ(capture)�������ޱ�����(QEP)��·����˷ḻ�Ĺ����������ڶ�̬����(motion control)���������(motor control)��Ӧ�á����9��ʾ���������¼�����ģ��(EVA��EVB)

����ͬ����Χ���ܹ�����2������綯��������Ӧ���ڶ��ᶯ̬���ơ�

ͼ8�¼�����ģ��(EVA)֮���ܷ���ͼ��

��9�¼�����ģ����ź����ƣ�

2.5.1�������ȵ���(PWM)

PWM�Ĺ��ܰ�����

1.ӵ�п���ɳ����Dead-time���ȡ�

2.PWM�ز�Ƶ��ʵʱ�ĸı䡣

3.PWM��������ʵʱ�ĸı䡣

4.�����������������ǶԳơ��ԳƼ��ռ�����PWM�źš�

5.�ṩ�ⲿ�����ӽ�PDPINTx���������ʼ��壬������ӽ�Ϊ��LOW��ʱ��PWM�źŽ���ǿ�Ʊ�Ϊ���迹.��ͼ9��ʾΪPWM ��·�ķ���ͼ���䶯�����̴���Ϊ���Ƚ�����ֵ(CMPRx)������T1CON���趨�ĶԳƻ�ǶԳ�֮���αȽϣ�Ȼ���������PHx�������Dead-time ������·������������

Dead-time���źţ������������·���趨ÿ��PWM�����������˾Ϳɲ�������Ҫ��PWM�źš�

ͼ9 PWM ��·����ͼ

��ͼ10 ��ʾΪ�ǶԳ�PWM ����ͼ������PWM1��PWM3��PWM5�������ΪActive High��PWM2��PWM4��PWM6 �������ΪActiveLow������趨Dead-time ��ʹ��PWMx ��PWMX+1 ��Ѷ�Ų�ͬʱΪHigh��������IGBT ΪActive High ֮���ʼ��塣

ͼ10�ǶԳ�PWM�źŲ���ͼ(x=1,3,or5)��

��ͼ11��ʾΪ�Գ�PWM����ͼ������PWM1��PWM3��PWM5 �������ΪActiveLow��PWM2��PWM4��PWM6�������ΪActiveHigh������趨Dead-time��ʹ��PWMx��PWMX+1���źŲ�ͬʱΪLow��������IGBTΪActiveLow֮���ʼ��壬��ϵͳ����������趨��ʽ��

ͼ11�Գ�PWM�źŲ���ͼ(x=1,3,or5)��

2.5.2QEP��Ԫ

ÿ���¼�����ģ�鶼��һ�������ޱ��������·(QEP��·)��ʹ���߿��Խ��������·����������������90�ȵ��ź��͵�EVA ��CAP1/QEP1��CAP2/QEP2��EVB��CAP4/QEP3��CAP5/QEP4����ȡ��λ�����ٶȵ���Ϣ��F2812�ܹ���EVA��EVB ߢȡ����Encoder���źš�EVA��QEP��·��GPtimer2ΪƵ�ʻ�������EVB��QEP��·��GPtimer4ΪƵ�ʻ�������F240 ���IJ����������ϲ�����16λ�Ķ�ʱ������չ��32λ�Ķ�ʱ����ֻ����16λ�Ķ�ʱ����ʹ�á�QEP ��·�Ķ�ʱ��֮����ģʽ��������ڡ�����������/��������ģʽ����EVA��QEP��·����ͼ��ͼ12��ʾ��EVB��QEP��·����ͼ��ͼ13��ʾ��

ͼ12EVA��QEP��·����ͼ��

ͼ13EVB��QEP��·����ͼ��

��ͼ14��ʾΪ���͵�Encoder����źţ���ͼ����벿������QEP1����QEP2Ϊ90 �ȣ����Զ�ʱ��ʹ�������͡���ͼ���Ұ벿������QEP2����QEP1Ϊ90�ȣ����Զ�ʱ��ʹ�������͡�

ͼ14QEP�Ľ�aʱ����ͼ��

2.6ͨ������/���(GPIO)�ӿ�

ͼ15ΪGPIO�ķ���ͼ��F2812������Χ����GPIO�����ӽţ�ʹ��ʱ��Ҫ�趨GPxMUX��GPxDIR��GPxQUAL��GPxDAT �Ȼ��������ﵽӲ���ϵ����á�

GPxMUX��ÿ��I/O�˿ڶ���һ����������(GPxMUX)��GPxMUX ������������ѡ����Щ�ӽű�������������I/O(GPxMUX.bit=0)������ΧI/O(GPxMUX.bit=1)����DSP����ʱ������I/O Ԥ��Ϊ��λI/O��

GPxDIR��ÿ��I/O�˿ڶ���һ��������ƻ�����(GPxDIR)�������趨Ϊ����I/Oʱ����ӽ�Ϊ����(GPxDIR.bit= 0)�����(GPxDIR.bit=1)����DSP

����ʱ������I/OԤ��Ϊ����I/O��

GPxQUAL������ȡ�����ƻ������������趨��Ϊ����I/O����(INPUT)

ʱ�������ϵ�ȡ���ʡ�

GPxDAT��ÿ��I/O�˿ڶ���һ�����ݻ�����(GPxDAT)��������д�ӽŵ�״̬��

ͼ15 GPIO����ͼ��

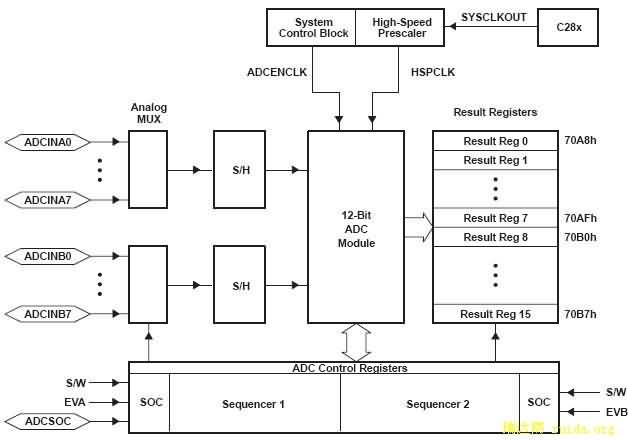

2.7ģ������ת��(Analog-to-DigitalConverter,ADC)ģ��ͼ16ΪADCģ�顣ADCģ������ڽ���ȡ��/ ����(sample-and-hold,S/H)��12-bitADC��ADCģ�鹦�ܰ�����

1.�ڽ�ȡ��/����(sample-and-hold,S/H)֮12λADC����

2.ģ�����뷶Χ��0.0V~3.0V

3.����ת�����ʣ�80nsat25-MHz ADC clock,12.5 MSPS

4.��16ͨ��(channels)�Ķ���������

ȡ������ģ���ѹ֮���ֵ�ѹֵ��

12-bit��ADCģ����25-MHzADCƵ����80ns֮����ת����ADCģ����16���ŵ��������趨������������8 �ŵ�ģ���������¼�����(EVA,EVB)��

ͼ16ADCģ�鷽��ͼ��

��ͼ17��ʾΪTI����֮����ͼ��������ADCģ���Ƶ�ʲ�����1~18.75MHzʱADCRESEXT �ĵ���ƫѹ����ʹ��24.9K������������18.75MHz~25MHz��ADCRESEXT�ĵ���ƫѹ����ʹ��20K������2812��

λ���ư�֮ADCģ��ϣ��������25MHz��������ʹ��20K������ƫѹ���衣

ͼ17ADC�ܽ�֮���ӡ�

2.8����ͨѶ�ӿ�(SerialCommunicationsInterface,SCI)ģ��

F2812��ͼ18��ʾ������������ͨѶ�ӿ�(SCI)ģ�飬SCIģ���ṩ��DSP ��������non-return-to-zero(NRZ)��ʽ���첽��Χ֮�������ͨѶ��SCI �Ľ����ߺʹ����߽Բ���˫����ģʽ(Double-Buffered)��ÿһ���������Ѷ��Ե��������ж�λ��Ϊ�˱�֤���ݵ������ԣ�SCI���ж���⡢

ͬλ��⡢���غͿ�ܴ���ȥ�����ս��������ݡ�SCIģ����Ҫ�Ĺ�����

����ʾ��

1.�����ⲿ������λ

��SCITXD��SCI�����������λ

��SCIRXD��SCI������������λ

2.������64K�ֲ�ͬ�����ʣ��ɽ��ɻ������趨�ı䴫������

3.�����ַ�(Data-word)��ʽ

��һ����ʼλ

����������λ���ȸ�ʽ���ɴ�1��8֮��������ѡ��

����ͬλ���/żͬλ���/��ʹ��ͬλ����ѡ��

����ѡ��1��2��ֹͣλ

4.���ִ��������꣺ͬλ(Parity)������(Overrun)�����(Framing)����

��(Break)�������

5.��ѡ��ʹ�ð�˫������ȫ˫������ģʽ

6.���պ��봫��Բ���˫����ģʽ(Double-buffered)

7.���䷽������NRZ(non-return-to-zero)��ʽ

ͼ18����ͨѶ�ӿ�(SCI)ģ��֮����ͼ��

��ǿ��SCI����ɫ��

�Զ��������Ӳ����

16-level����/����FIFO

2.9������Χ�ӿ�(SerialPeripheralInterface,SPI)ģ��

F2812��ͼ19��ʾ����������λ������Χ�ӿ�(SPI)ģ�顣SPI ģ��ʹ����DSP���������ⲿ��Χ����һ������������֮һ��ͨѶ�����͵�Ӧ�ð����ⲿI/O ����Χ����װ�ã����磺��λ����������ʾװ�ú�ADCs��SPI֮Master/Slave����֧�ֶ���װ��ͨѶ��

SPIģ��װ����Ҫ���ܹ�������������

1.�ĸ��ⲿ����λ��

��SPISOMI��SPIslave-���/master-��������λ

��SPISIMO��SPIslave-����/master-�������λ

��SPISTE��SPIslave����-��������λ

��SPICLK��SPI����-Ƶ������λ

2.��������ģʽ��Master��Slave

3.���ʣ�125����ͬ�ɳ�������

4.�����ַ�(Data-word)���ȣ�1��16������λ��ǿ��SPI����ɫ��

16-level����/����FIFO

�ӳٴ��ݿ���

ͼ19������Χ�ӿ�(SPI)ģ��֮����ͼ��

2.10Bootloader����ģʽ

TMS320F2812��оƬ�ṩ���ֵ�Boot����ģʽ��ʹ����ѡ���ʹ�ã���һС����Ҫ����Boot����ģʽ�ķ��������10ΪBoot ����ģʽ����GPIOF�е��ĸ��ӽ�(GPIOF2��3��4��12)�ڿ���ʱ��״̬��ѡ�����ֵĿ���������

��10Bootģʽ֮GPIOF����λ״̬��

GPIOF4 (SCITXDA) GPIOF12 (MDXA) GPIOF3 (SPISTEA) GPIOF2 (SPICLK) ģʽѡ�� (Mode Selected) 1 X X X ��Flash��ַ (0x3F7FF6) 0 1 X X ���ⲿEEPROM����SPI_Boot����0 0 1 1 ��SCI-A���� SCI_Boot ���� 0 0 1 0 ��H0 SARAM��ַ (0x3F8000) 0 0 0 1 ��OTP��ַ(0x3D7800) 0 0 0 0 ��GPIOB����Parallel_Boot����

ͼ20Bootloaderģʽ����ͼ��

��ͼ20ΪBootloaderģʽ����ͼ��������Bootloaderģʽ������

1.��FlashMemory��

�����ģʽ�У�DSP������ȥִ���ڲ���FlashMemory��ַ(0x3F7FF6)������ʹ���߱�����0x3F7FF6�����ַ��¼һ������Boot ������Ļ�е�룬�磺LB_c_int00��

2.��H0SARAM��

�����ģʽ�У�BootROM�������趨F2812װ��Ȼ��ֱ����ȥ��ַ0x3F8000(��H0SARAM�ڴ淽��ĵ�һ����ַ)��

3.��OTP�ڴ棺

�����ģʽ�У�BootROM�������趨F2812װ��Ȼ��ֱ����ȥ��ַ0x3D7800(��OTP�ڴ淽��֮��һ����ַ)��

4.������Bootģʽ(SCI)��

�����ģʽ�У�����SCI-A�˿ڼ��س�����뵽on-chip�ڴ��ִ�����ڴ���ִ��Boot����

5.SPIEEPROMBootģʽ��

�����ģʽ�У�����SPI�����ⲿEEPROM���س����������ݵ�on-chip�ڴ��

6.��GPIO��Boot��

�����ģʽ�У�����GPIOB���ⲿ�����س����������ݣ����ģʽ�ֱ�֧��8λ��16λ�����ݴ���

����������ȷӦ������Ӣ��ԭ��������ϲ���

R:��ȡ;R/W:�ɶ���д;-0=���ú��ֵ

NOTE:EALLOW-protected register

��6 LOSPCP ������λԪ˵������

λԪ ����

��������

15-3 Reserved ���� 2-0 LSPCLK��ЩλԪ�趨������ΧƵ�ʱ�(LSPCLK)��SYSCLKOUT�Ĺ�ϵ�����LOSPCP��0��LSPCLK=SYSCLKOUT/(LOSPCPx2)

���LOSPCP=0��LSPCLK =SYSCLKOUT

=000������Ƶ��= SYSCLKOUT/1

=001������Ƶ��= SYSCLKOUT/2

=010������Ƶ��= SYSCLKOUT/4( Ԥ��ֵ)

=011 ������Ƶ��= SYSCLKOUT/6

=100������Ƶ��= SYSCLKOUT/8

=101������Ƶ��= SYSCLKOUT/10

=110 ������Ƶ��= SYSCLKOUT/12

=111 ������Ƶ��= SYSCLKOUT/14

PCLKCR(��ΧƵ�ʿ��ƻ�����)��������������ܸ�����Χģ���Ƶ�ʣ�����ΧҪʹ��ʱ�ͱ��轫��Ƶ�����������һ����Χ����ʹ�ã���������ʹ�õ���Χ�����Խ���Ƶ�ʹص�����˿��Դﵽ��ʡ���ʵ����á����7 ��ʾΪPCLKCR�������ĸ�ʽ����������λԪ˵�����8��ʾ��

��7PCLKCR������λԪ��ʽ��*��

15 14 13 12 11 10 9 8 Reserved ECAN ENCLK Reserved MCBSP ENCLK SCIB ENCLK SCIA ENCLK Reserved SPI ENCLK R-0 R/W-0 R-0 R/W-0 R/W-0 R/W-0 R-0 R/W-0

7-4 3 2 1 0 Reserved ADC ENCLK Reserved EVB ENCLK EVA ENCLK R-0 R/W-0 R-0 R/W-0 R/W-0

R:��ȡ;R/W:�ɶ���д;-0=���ú��ֵ

NOTE:EALLOW-protected register

*�����Χ����û��ʹ�ã������Χ��Ƶ�ʽ����Ա��ص��Ѵ����С�ĵ�������

��8PCLKCR������λԪ˵������

λԪ ����

��������

15 Reserved ����14 ECAN ENCLK �����λԪ���趨����CAN ��Χ��Χ�ڵ�ϵͳƵ�ʽ� �����ܡ��ڵ͵��������£���λ����ʹ����������Ϊ0�� 13 Reserved ���� 12 MCBSP ENCLK �����λԪ���趨����McBSP��Χ��Χ�ڵĵ���Ƶ��(LSPCLK)�������ܡ��ڵ͵��������£���λ����ʹ������������Ϊ0�� 11 SCIB ENCLK �����λԪ���趨����SCI-B ��Χ��Χ�ڵĵ���Ƶ��(LSPCLK)�������ܡ��ڵ͵��������£���λԪ����ʹ������������Ϊ0�� 10 SCIA ENCLK �����λԪ���趨����SCI-A ��Χ��Χ�ڵĵ���Ƶ��(LSPCLK)�������ܡ��ڵ͵��������£���λ����ʹ������������Ϊ0�� 9 Reserved ���� 8 SPIA ENCLK �����λԪ���趨����SPI ��Χ��Χ�ڵĵ���Ƶ��(LSPCLK)�������ܡ��ڵ͵��������£���λ����ʹ������������Ϊ0�� 7-4 Reserved ���� 3 ADC ENCLK �����λԪ���趨����ADC ��Χ��Χ�ڵĸ���Ƶ��(HSPCLK)�������ܡ��ڵ͵��������£���λ����ʹ������������Ϊ0��2 Reserved ���� 1 EVB ENCLK �����λԪ���趨����EV-B ��Χ��Χ�ڵĸ���Ƶ��(HSPCLK)�������ܡ��ڵ͵��������£���λ����ʹ������������Ϊ0�� 0 EVA ENCLK �����λԪ���趨����EV-A ��Χ��Χ�ڵĸ���Ƶ��(HSPCLK)�������ܡ��ڵ͵��������£���λ����ʹ������������Ϊ0��2.3�ڴ�ṹ����

2.3.1TMS320F2812�ڴ�ӳ

��ͼ4ΪTMS320F2812�ڴ�ӳ��Low64K��֮�ڴ��ַ��Χӳ��240x�����ݿռ��ַ����High 64K��֮�ڴ��ַ��Χӳ��24x/240x�ij���ռ��ַ��24x/240x���ݳ������ֻ���ڡ�High64K���ڴ�����ִ�С�

ͼ4TMS320F2812�ڴ�ӳ��(MemoryMap)��

17

2.3.2�ⲿ�ڴ�ӿ�(XINTF)

TMS320F2812���ⲿ�ڴ�ӿ�(XINTF)�ǷǶ������첽���ߣ�ӳ��5���̶����ڴ�ӳ�����Σ��䶨����ͼ5 ��ʾ.�ⲿ�ڴ�ӿ�(XINTF)�ṩ19����ַ��16�������ߣ�ÿ��������

����Դ�ȡ���ڴ淶ΧΪ512Kx16����֧�ֵ��ⲿ�ڴ�ߴ�1Mx16

���ϡ�

ͼ5�ⲿ�ڴ�ӿ�(XINTF)����ͼ��

2.4 32λԪCPU Timers0/1/2

TMS320F2812��3��32λԪ��CPUTimer����ͼ7ΪCPU-Timers֮����ͼ��CPU-Timer0 ������ʹ������Ӧ�ã���CPU-Timer1��CPU-Timer2������Ϊʵʱ(Real-Time)OS(���磺DSP-BIOS)����ЩCPU-Timers ��ͬ���¼�����ģ��(EVA,EVB)��һ����;��(General-Purpose)Timers��CPU-Timer�����ϵ��������£�32 λԪ�ļ���������(TIMH��TIM)�������ڻ�����(PRDH��PRD)��ֵ����������������TMS320F2812��SYSCLKOUT(150MHz)֮���ʵݼ�����������0ʱ��Timer�����һ���ж��źš�

���IC����

LC864512��5C77/N801 LA7687A��N201�� LA4285(N

AN5195K��AN5199��AN5265��AN5274��AN5521��AN5

AD9883APDF��ʽ�ο����ϡ�

BA3880S��BA7001��BA7021��PDF��ʽ�ο�����

CTV222S��PDF��ʽ�ο�����

CXP84420-X133SP��PDF��ʽ�ο�����

KA9258D��PDF��ʽ�ο�����

LA4225��LA4285��LA4287��LA7680��LA7688A��LA7

LC863320A��LC864912A��LC864916A����PDF��ʽ��

M51393AP�����